# AMD Athlon<sup>™</sup> Processor x86 Code Optimization Guide

Publication No. Revision Date

22007 K February 2002

#### © 2001, 2002 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### **Trademarks**

AMD, the AMD Arrow logo, AMD Athlon, and combinations thereof, 3DNow!, AMD-751, and Super7 are trademarks, and AMD-K6 and AMD-K6-2 are registered trademarks of Advanced Micro Devices, Inc.

Microsoft, Windows, and Windows NT are registered trademarks of Microsoft Corporation.

MMX is a trademark and Pentium is a registered trademark of Intel Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# **Contents**

|           | List of Figures                                                                                                                                                                                                                        |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | List of Tables                                                                                                                                                                                                                         |

|           | Revision History                                                                                                                                                                                                                       |

| Chapter 1 | Introduction                                                                                                                                                                                                                           |

|           | About This Document                                                                                                                                                                                                                    |

|           | AMD Athlon™ Processor Family                                                                                                                                                                                                           |

|           | AMD Athlon Processor Microarchitecture Summary 4                                                                                                                                                                                       |

| Chapter 2 | Top Optimizations 7                                                                                                                                                                                                                    |

|           | Optimization Star                                                                                                                                                                                                                      |

|           | Group I Optimizations—Essential Optimizations                                                                                                                                                                                          |

|           | Group II Optimizations—Secondary Optimizations                                                                                                                                                                                         |

|           | Load-Execute Instruction Usage10Take Advantage of Write Combining12Optimizing Main Memory Performance for Large Arrays12Use 3DNow! Instructions13Recognize 3DNow! Professional Instructions14Avoid Branches Dependent on Random Data14 |

|           | Avoid Placing Code and Data in the Same 64-Byte Cache Line 15                                                                                                                                                                          |

Table of Contents iii

| Chapter 3 | C Source-Level Optimizations                                      |

|-----------|-------------------------------------------------------------------|

|           | Ensure Floating-Point Variables and Expressions are of Type Float |

|           | Use 32-Bit Data Types for Integer Code                            |

|           | Consider the Sign of Integer Operands                             |

|           | Use Array-Style Instead of Pointer-Style Code                     |

|           | Completely Unroll Small Loops                                     |

|           | Avoid Unnecessary Store-to-Load Dependencies                      |

|           | Always Match the Size of Stores and Loads                         |

|           | Consider Expression Order in Compound Branch Conditions 27        |

|           | Switch Statement Usage                                            |

|           | Use Prototypes for All Functions                                  |

|           | Use Const Type Qualifier                                          |

|           | Generic Loop Hoisting                                             |

|           | Declare Local Functions as Static                                 |

|           | Dynamic Memory Allocation Consideration                           |

|           | Introduce Explicit Parallelism into Code                          |

|           | Explicitly Extract Common Subexpressions                          |

|           | C Language Structure Component Considerations                     |

|           | Sort Local Variables According to Base Type Size                  |

|           | Accelerating Floating-Point Divides and Square Roots              |

|           | Fast Floating-Point-to-Integer Conversion                         |

|           | Speeding Up Branches Based on Comparisons Between Floats 42       |

|           | Avoid Unnecessary Integer Division                                |

|           | Copy Frequently Dereferenced Pointer Arguments to Local Variables |

|           | Use Block Prefetch Optimizations                                  |

*iv* Table of Contents

| Chapter 4 | Instruction Decoding Optimizations                                                   |

|-----------|--------------------------------------------------------------------------------------|

|           | Overview                                                                             |

|           | Select DirectPath Over VectorPath Instructions 50                                    |

|           | Load-Execute Instruction Usage                                                       |

|           | Use Load-Execute Integer Instructions50                                              |

|           | Use Load-Execute Floating-Point Instructions with Floating-Point Operands            |

|           | Avoid Load-Execute Floating-Point Instructions with Integer Operands                 |

|           | Use Read-Modify-Write Instructions Where Appropriate 52                              |

|           | Align Branch Targets in Program Hot Spots 54                                         |

|           | Use 32-Bit LEA Rather than 16-Bit LEA Instruction 54                                 |

|           | Use Short Instruction Encodings                                                      |

|           | Avoid Partial-Register Reads and Writes 55                                           |

|           | Use LEAVE Instruction for Function Epilogue Code                                     |

|           | Replace Certain SHLD Instructions with Alternative Code 57                           |

|           | Use 8-Bit Sign-Extended Immediates                                                   |

|           | Use 8-Bit Sign-Extended Displacements                                                |

|           | Code Padding Using Neutral Code Fillers                                              |

|           | Recommendations for AMD-K6 <sup>®</sup> Family and AMD Athlon Processor Blended Code |

Table of Contents v

| Chapter 5 | Cache and Memory Optimizations                             | 63 |

|-----------|------------------------------------------------------------|----|

|           | Memory Size and Alignment Issues                           | 63 |

|           | Avoid Memory-Size Mismatches                               | 63 |

|           | Align Data Where Possible                                  | 65 |

|           | Optimizing Main Memory Performance for Large Arrays        | 66 |

|           | Memory Copy Optimization                                   | 67 |

|           | Array Addition                                             | 74 |

|           | Summary                                                    | 78 |

|           | Use the PREFETCH 3DNow! <sup>TM</sup> Instruction          | 79 |

|           | Determining Prefetch Distance                              | 83 |

|           | Take Advantage of Write Combining                          | 85 |

|           | Avoid Placing Code and Data in the Same 64-Byte Cache Line | 85 |

|           | Multiprocessor Considerations                              | 86 |

|           | Store-to-Load Forwarding Restrictions                      | 86 |

|           | Store-to-Load Forwarding Pitfalls—True Dependencies        | 87 |

|           | Summary of Store-to-Load Forwarding Pitfalls to Avoid      | 90 |

|           | Stack Alignment Considerations                             | 90 |

|           | Align TBYTE Variables on Quadword Aligned Addresses        | 91 |

|           | C Language Structure Component Considerations              | 91 |

|           | Sort Variables According to Base Type Size                 | 92 |

vi Table of Contents

| Chapter 6 | Branch Optimizations                                            | 93  |

|-----------|-----------------------------------------------------------------|-----|

|           | Avoid Branches Dependent on Random Data                         | 93  |

|           | AMD Athlon Processor Specific Code                              | 94  |

|           | Blended AMD-K6 and AMD Athlon Processor Code                    | 94  |

|           | Always Pair CALL and RETURN                                     | 96  |

|           | Recursive Functions                                             | 97  |

|           | Replace Branches with Computation in 3DNow! Code                | 98  |

|           | Muxing Constructs                                               | 98  |

|           | Sample Code Translated into 3DNow! Code                         | 100 |

|           | Avoid the Loop Instruction                                      | 104 |

|           | Avoid Far Control Transfer Instructions                         | 104 |

| Chapter 7 | Scheduling Optimizations                                        | 105 |

|           | Schedule Instructions According to their Latency                | 105 |

|           | Unrolling Loops                                                 | 106 |

|           | Complete Loop Unrolling                                         | 106 |

|           | Partial Loop Unrolling                                          | 106 |

|           | Use Function Inlining                                           | 109 |

|           | Overview                                                        | 109 |

|           | Always Inline Functions if Called from One Site                 | 110 |

|           | Always Inline Functions with Fewer than 25 Machine Instructions | 110 |

|           | Avoid Address Generation Interlocks                             | 110 |

|           | Use MOVZX and MOVSX                                             | 111 |

|           | Minimize Pointer Arithmetic in Loops                            | 112 |

|           | Push Memory Data Carefully                                      | 114 |

|           |                                                                 |     |

Table of Contents vii

| Chapter 8 | Integer Optimizations115                                                            |

|-----------|-------------------------------------------------------------------------------------|

|           | Replace Divides with Multiplies                                                     |

|           | Multiplication by Reciprocal (Division) Utility116                                  |

|           | Unsigned Division by Multiplication of Constant                                     |

|           | Consider Alternative Code When Multiplying by a Constant 120                        |

|           | Use MMX™ Instructions for Integer-Only Work                                         |

|           | Repeated String Instruction Usage                                                   |

|           | Latency of Repeated String Instructions                                             |

|           | Use XOR Instruction to Clear Integer Registers                                      |

|           | Efficient 64-Bit Integer Arithmetic                                                 |

|           | Efficient Implementation of Population Count Function 136                           |

|           | Efficient Binary-to-ASCII Decimal Conversion                                        |

|           | Derivation of Multiplier Used for Integer Division by Constants . 144               |

|           | Derivation of Algorithm, Multiplier, and Shift Factor for Unsigned Integer Division |

|           | Integer Division148                                                                 |

*Viii* Table of Contents

| Chapter 9  | Floating-Point Optimizations                                             |

|------------|--------------------------------------------------------------------------|

|            | Ensure All FPU Data is Aligned                                           |

|            | Use Multiplies Rather than Divides                                       |

|            | Use FFREEP Macro to Pop One Register from the FPU Stack 152              |

|            | Floating-Point Compare Instructions                                      |

|            | Use the FXCH Instruction Rather than FST/FLD Pairs                       |

|            | Avoid Using Extended-Precision Data                                      |

|            | Minimize Floating-Point-to-Integer Conversions 154                       |

|            | Check Argument Range of Trigonometric Instructions Efficiently 15        |

|            | Take Advantage of the FSINCOS Instruction                                |

| Chapter 10 | 3DNow!™ and MMX™ Optimizations                                           |

|            | Use 3DNow! Instructions                                                  |

|            | Use FEMMS Instruction                                                    |

|            | Use 3DNow! Instructions for Fast Division                                |

|            | Optimized 14-Bit Precision Divide                                        |

|            | Optimized Full 24-Bit Precision Divide                                   |

|            | Newton-Raphson Reciprocal                                                |

|            | Use 3DNow! Instructions for Fast Square Root and Reciprocal Square Root  |

|            | Optimized 15-Bit Precision Square Root                                   |

|            | Optimized 24-Bit Precision Square Root                                   |

|            | Newton-Raphson Reciprocal Square Root                                    |

|            | Use MMX PMADDWD Instruction to Perform Two 32-Bit Multiplies in Parallel |

|            | Use PMULHUW to Compute Upper Half of Unsigned Products 16                |

|            | 3DNow! and MMX Intra-Operand Swapping 169                                |

|            | Fast Conversion of Signed Words to Floating-Point                        |

Table of Contents ix

|            | Width of Memory Access Differs Between PUNPCKL* and PUNPCKH*      | 71         |

|------------|-------------------------------------------------------------------|------------|

|            | Use MMX PXOR to Negate 3DNow! Data                                | 72         |

|            | Use MMX PCMP Instead of 3DNow! PFCMP                              | 73         |

|            | Use MMX Instructions for Block Copies and Block Fills 17          | 74         |

|            | Efficient 64-Bit Population Count Using MMX Instructions 18       | 34         |

|            | Use MMX PXOR to Clear All Bits in an MMX Register 18              | 35         |

|            | Use MMX PCMPEQD to Set All Bits in an MMX Register 18             | 36         |

|            | Use MMX PAND to Find Floating-Point Absolute Value in 3DNow! Code | 36         |

|            | Integer Absolute Value Computation Using MMX Instructions 18      | 36         |

|            | Optimized Matrix Multiplication                                   | 37         |

|            | Efficient 3D-Clipping Code Computation Using 3DNow! Instructions  | 90         |

|            | Efficiently Determining Similarity Between RGBA Pixels 19         | )2         |

|            | Use 3DNow! PAVGUSB for MPEG-2 Motion Compensation 19              | )5         |

|            | Efficient Implementation of floor() Using 3DNow! Instructions 19  | <b>)</b> 7 |

|            | Stream of Packed Unsigned Bytes                                   | 98         |

|            | Complex Number Arithmetic                                         | <b>)</b> 9 |

| Chapter 11 | General x86 Optimization Guidelines20                             | )1         |

|            | Short Forms                                                       | )1         |

|            | Dependencies                                                      | )2         |

|            | Register Operands                                                 | )2         |

|            | Stack Allocation                                                  | )2         |

|            |                                                                   |            |

X Table of Contents

| Appendix A | AMD Athlon™ Processor Microarchitecture        | 203         |

|------------|------------------------------------------------|-------------|

|            | Introduction                                   | 203         |

|            | AMD Athlon Processor Microarchitecture         | 204         |

|            | Superscalar Processor                          | 204         |

|            | Instruction Cache                              |             |

|            | Predecode                                      | 206         |

|            | Branch Prediction                              | 206         |

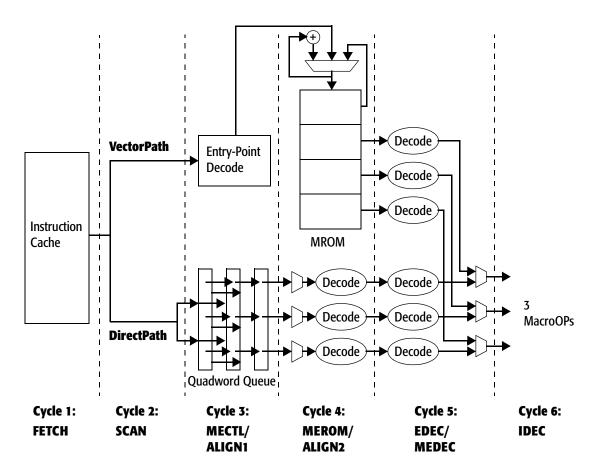

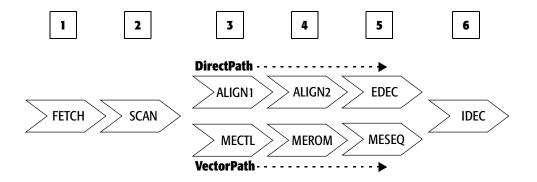

|            | Early Decoding                                 | 207         |

|            | Instruction Control Unit                       | 208         |

|            | Data Cache                                     | 208         |

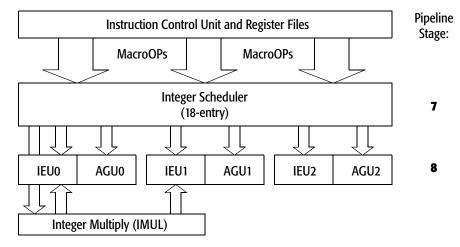

|            | Integer Scheduler                              | 209         |

|            | Integer Execution Unit                         | <b>20</b> 9 |

|            | Floating-Point Scheduler                       | 210         |

|            | Floating-Point Execution Unit                  | 211         |

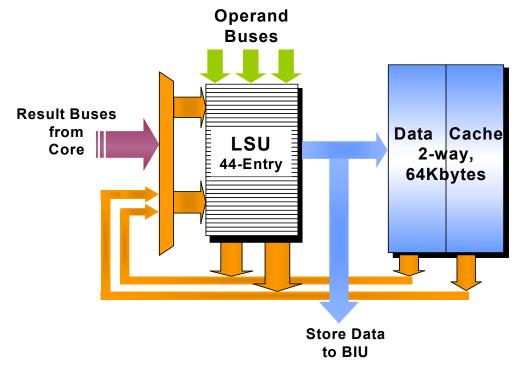

|            | Load-Store Unit (LSU)                          | 212         |

|            | L2 Cache                                       | 213         |

|            | Write Combining                                | 213         |

|            | AMD Athlon System Bus                          | 214         |

| Appendix B | Pipeline and Execution Unit Resources Overview | 215         |

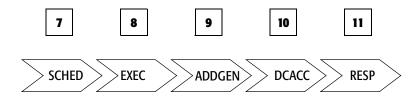

|            | Fetch and Decode Pipeline Stages               | 215         |

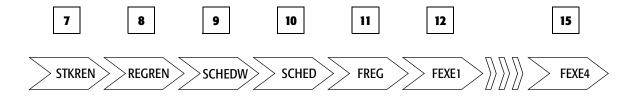

|            | Integer Pipeline Stages                        | 218         |

|            | Floating-Point Pipeline Stages                 | 220         |

|            | Execution Unit Resources                       | 222         |

|            | Terminology                                    | 222         |

|            | Integer Pipeline Operations                    | <b>22</b> 3 |

|            | Floating-Point Pipeline Operations             | 224         |

|            | Load/Store Pipeline Operations                 | 225         |

|            | Code Sample Analysis                           |             |

|            |                                                |             |

Table of Contents xi

| Appendix C | Implementation of Write Combining                                   | 229   |

|------------|---------------------------------------------------------------------|-------|

|            | Introduction                                                        | 229   |

|            | Write-Combining Definitions and Abbreviations                       | 230   |

|            | What is Write Combining?                                            | 230   |

|            | Programming Details                                                 | 230   |

|            | Write-Combining Operations  Sending Write-Buffer Data to the System |       |

| Appendix D | Performance-Monitoring Counters                                     | 235   |

|            | Overview                                                            | 235   |

|            | Performance Counter Usage                                           | 236   |

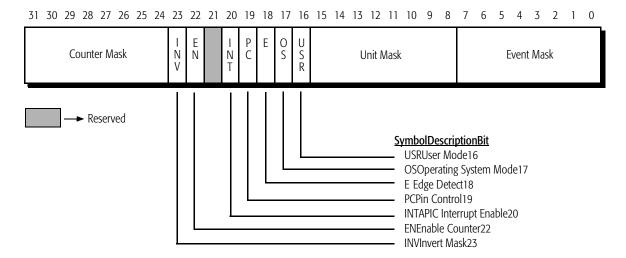

|            | PerfEvtSel[3:0] MSRs (MSR Addresses C001_0000h-C001_0003h 236       | l)    |

|            | PerfCtr[3:0] MSRs (MSR Addresses C001_0004h-C001_0007h) .           | . 240 |

| Appendix E | Programming the MTRR and PAT                                        | 243   |

|            | Introduction                                                        | 243   |

|            | Memory Type Range Register (MTRR) Mechanism                         | 243   |

|            | Page Attribute Table (PAT)                                          | 249   |

| Appendix F | Instruction Dispatch and Execution Resources/Timing                 | 259   |

| Index      |                                                                     | 305   |

*xii* Table of Contents

# **List of Figures**

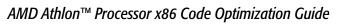

| Figure 1.  | AMD Athlon™ Processor Block Diagram       | 205 |

|------------|-------------------------------------------|-----|

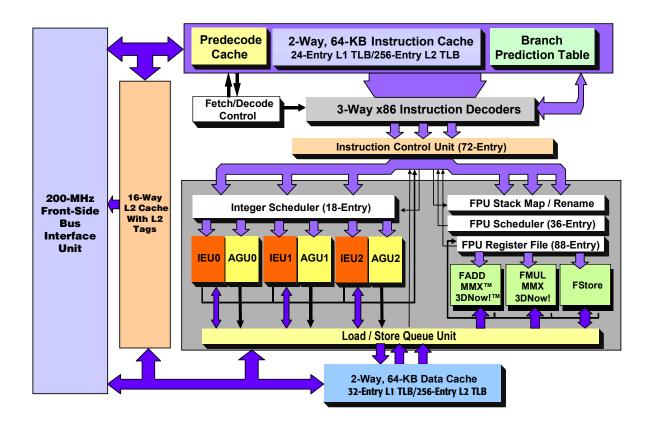

| Figure 2.  | Integer Execution Pipeline                | 209 |

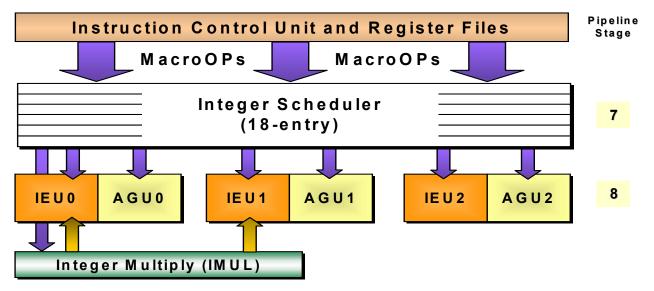

| Figure 3.  | Floating-Point Unit Block Diagram         | 211 |

| Figure 4.  | Load/Store Unit                           | 212 |

| Figure 5.  | Fetch/Scan/Align/Decode Pipeline Hardware | 216 |

| Figure 6.  | Fetch/Scan/Align/Decode Pipeline Stages   | 216 |

| Figure 7.  | Integer Execution Pipeline                | 218 |

| Figure 8.  | Integer Pipeline Stages                   | 218 |

| Figure 9.  | Floating-Point Unit Block Diagram         | 220 |

| Figure 10. | Floating-Point Pipeline Stages            | 220 |

| Figure 11. | PerfEvtSel[3:0] Registers                 | 237 |

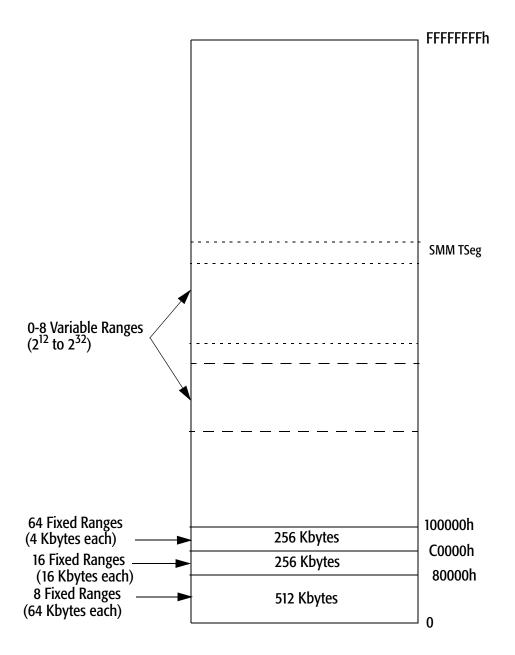

| Figure 12. | MTRR Mapping of Physical Memory           | 245 |

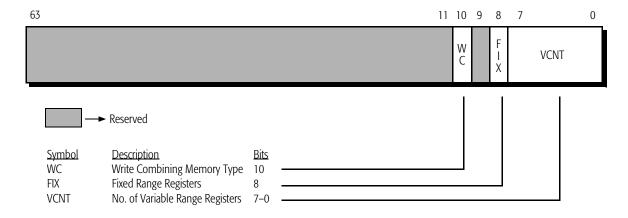

| Figure 13. | MTRR Capability Register Format           | 246 |

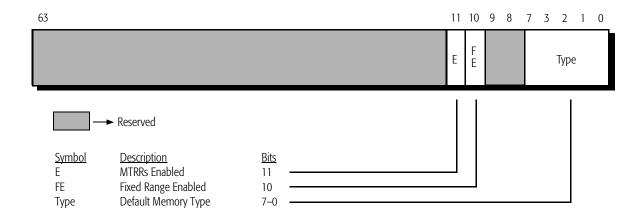

| Figure 14. | MTRR Default Type Register Format         | 247 |

| Figure 15. | Page Attribute Table (MSR 277h)           | 249 |

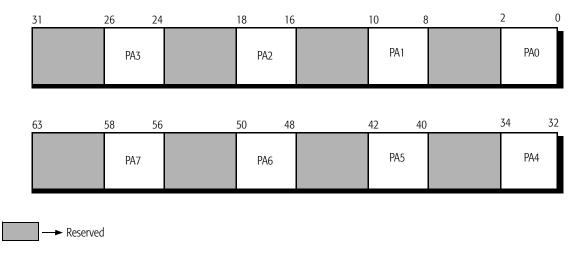

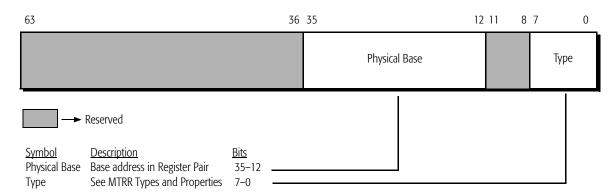

| Figure 16. | MTRRphysBasen Register Format             | 255 |

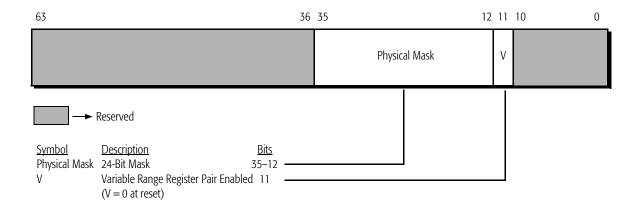

| Figure 17. | MTRRphysMaskn Register Format             | 256 |

List of Figures xiii

22007K February 2002

xiv List of Figures

# **List of Tables**

| Table 1.  | Latency of Repeated String Instructions                                          | 123   |

|-----------|----------------------------------------------------------------------------------|-------|

| Table 2.  | Integer Pipeline Operation Types                                                 | 223   |

| Table 3.  | Integer Decode Types                                                             | 223   |

| Table 4.  | Floating-Point Pipeline Operation Types                                          | 224   |

| Table 5.  | Floating-Point Decode Types                                                      | 224   |

| Table 6.  | Load/Store Unit Stages                                                           | 225   |

| Table 7.  | Sample 1—Integer Register Operations                                             | 227   |

| Table 8.  | Sample 2—Integer Register and Memory Load Operations                             | . 228 |

| Table 9.  | Write Combining Completion Events                                                | 232   |

| Table 10. | $AMD\ Athlon^{\scriptscriptstyleTM}\ System\ Bus\ Command\ Generation\ Rules.$ . | 233   |

| Table 11. | Performance-Monitoring Counters                                                  | 238   |

| Table 12. | Memory Type Encodings                                                            | 246   |

| Table 13. | Standard MTRR Types and Properties                                               | 248   |

| Table 14. | PATi 3-Bit Encodings                                                             | 250   |

| Table 15. | Effective Memory Type Based on PAT and MTRRs                                     | 251   |

| Table 16. | Final Output Memory Types                                                        | 252   |

| Table 17. | MTRR Fixed Range Register Format                                                 | 254   |

| Table 18. | MTRR-Related Model-Specific Register (MSR) Map                                   | 257   |

| Table 19. | Integer Instructions                                                             | 261   |

| Table 20. | MMX <sup>TM</sup> Instructions                                                   | 287   |

| Table 21. | MMX <sup>TM</sup> Extensions                                                     | 291   |

| Table 22. | Floating-Point Instructions                                                      | 292   |

| Table 23. | 3DNow! <sup>TM</sup> Instructions                                                | 298   |

| Table 24. | 3DNow! <sup>TM</sup> Extensions                                                  | 300   |

| Table 25. | Instructions Introduced with 3DNow! <sup>TM</sup> Professional                   | 301   |

List of Tables xv

22007K February 2002

xvi List of Tables

# **Revision History**

| Date          | Rev                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Feb.<br>2002  | К                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Corrected the code sequences labeled "by 13" and "by 21" in "Consider Alternative Code When Multiplying by a Constant" on page 120.                                                                                                                                                                                                                          |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Removed the outdated references to Appendix G.<br>Removed the blank pages at the end of Chapter 10, "3DNow!™ and MMX™ Optimizations."                                                                                                                                                                                                                        |  |  |  |

| July<br>2001  | Replaced memcpy example for arrays in "AMD Athlon™ Processor-Specific Code" on page 178.  Revised "PerfCtr[3:0] MSRs (MSR Addresses C001_0004h-C001_0007h)" on page 240.  Added Table 25, "Instructions Introduced with 3DNow!™ Professional," on page 301.  Updated the wording regarding the L2 cache in "L2 Cache" on page 213.  Added block copy/prefetch to "Optimizing Main Memory Performance for Large Arrays" on page 66.  Removed Appendix G. |                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| Sept.<br>2000 | I                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Corrected Example 1 under "Muxing Constructs" on page 98.                                                                                                                                                                                                                                                                                                    |  |  |  |

| June<br>2000  | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Added Appendix D, "Performance-Monitoring Counters."                                                                                                                                                                                                                                                                                                         |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Added more details to the optimizations in Chapter 2, "Top Optimizations." Further clarified the information in "Use Array-Style Instead of Pointer-Style Code" on page 20.                                                                                                                                                                                  |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Added the optimization, "Always Match the Size of Stores and Loads" on page 24.  Added the optimization, "Fast Floating-Point-to-Integer Conversion" on page 40.  Added the optimization, "Speeding Up Branches Based on Comparisons Between Floats" on page 42.  Added the optimization, "Use Read-Modify-Write Instructions Where Appropriate" on page 52. |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Further clarified the information in "Align Branch Targets in Program Hot Spots" on page 54.                                                                                                                                                                                                                                                                 |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Added the optimization, "Use 32-Bit LEA Rather than 16-Bit LEA Instruction" on page 54.                                                                                                                                                                                                                                                                      |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Added the optimization, "Use LEAVE Instruction for Function Epilogue Code" on page 56.                                                                                                                                                                                                                                                                       |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Added more examples to "Memory Size and Alignment Issues" on page 63.                                                                                                                                                                                                                                                                                        |  |  |  |

| April         | G                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Further clarified the information in "Use the PREFETCH 3DNow!™ Instruction" on page 79.                                                                                                                                                                                                                                                                      |  |  |  |

| 2000          |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Further clarified the information in "Store-to-Load Forwarding Restrictions" on page 86.                                                                                                                                                                                                                                                                     |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Changed epilogue code in Example 1 of "Stack Alignment Considerations" on page 90.                                                                                                                                                                                                                                                                           |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Added Example 8 to "Avoid Branches Dependent on Random Data" on page 93.                                                                                                                                                                                                                                                                                     |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Fixed comments in examples 1 and 2 of "Unsigned Division by Multiplication of Constant" on page 116.                                                                                                                                                                                                                                                         |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Revised code in "Algorithm: Divisors $1 \le d \le 2^{31}$ , Odd d" page 116 and "Algorithm: Divisors $2 \le d \le 2^{31}$ " on page 118.                                                                                                                                                                                                                     |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Added more examples to "Efficient 64-Bit Integer Arithmetic" on page 125.                                                                                                                                                                                                                                                                                    |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Fixed typo in the integer example and added an MMX <sup>™</sup> version in "Efficient Implementation of Population Count Function" on page 136.                                                                                                                                                                                                              |  |  |  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Added the optimization, "Efficient Binary-to-ASCII Decimal Conversion" on page 139.                                                                                                                                                                                                                                                                          |  |  |  |

Revision History xvii

| Date  | Rev        | Description                                                                                                                                                                                                                                        |  |  |  |

|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|       | G<br>cont. | Updated the code in "Derivation of Multiplier Used for Integer Division by Constants" on page 144 and in the AMD Software Development Kit (SDK).                                                                                                   |  |  |  |

|       |            | Further clarified the information in "Use FFREEP Macro to Pop One Register from the FPU Stack" on page 152.                                                                                                                                        |  |  |  |

|       |            | Corrected Example 1 in "Minimize Floating-Point-to-Integer Conversions" on page 154.                                                                                                                                                               |  |  |  |

|       |            | Added the optimization, "Use PMULHUW to Compute Upper Half of Unsigned Products" on page 167.                                                                                                                                                      |  |  |  |

| April |            | Added "Width of Memory Access Differs Between PUNPCKL* and PUNPCKH*" on page 171. Rewrote "Use MMX™ Instructions for Block Copies and Block Fills" on page 174.                                                                                    |  |  |  |

| 2000  |            | Added the optimization, "Integer Absolute Value Computation Using MMX™ Instructions" on page 186.                                                                                                                                                  |  |  |  |

|       |            | Added the optimization, "Efficient 64-Bit Population Count Using MMX™ Instructions" on page 184.                                                                                                                                                   |  |  |  |

|       |            | Added the optimization, "Efficiently Determining Similarity Between RGBA Pixels" on page 192.                                                                                                                                                      |  |  |  |

|       |            | Added the optimization, "Efficient Implementation of floor() Using 3DNow!™ Instructions" on page 197.                                                                                                                                              |  |  |  |

|       |            | Corrected the instruction mnemonics for AAM, AAD, BOUND, FDIVP, FMULP, FDUBP, DIV, IDIV, IMUL, MUL, and TEST in "Instruction Dispatch and Execution Resources/Timing" on page 259 and in "Direct-Path versus VectorPath Instructions" on page 301. |  |  |  |

|       |            | Added "About This Document" on page 1.                                                                                                                                                                                                             |  |  |  |

|       |            | Further clarified the information in "Consider the Sign of Integer Operands" on page 18.                                                                                                                                                           |  |  |  |

|       | E          | Added the optimization, "Use Array-Style Instead of Pointer-Style Code" on page 20.                                                                                                                                                                |  |  |  |

|       |            | Added the optimization, "Accelerating Floating-Point Divides and Square Roots" on page 38.                                                                                                                                                         |  |  |  |

|       |            | Clarified the examples in "Copy Frequently Dereferenced Pointer Arguments to Local Variables" on page 44.                                                                                                                                          |  |  |  |

|       |            | Further clarified the information in "Select DirectPath Over VectorPath Instructions" on page 50.                                                                                                                                                  |  |  |  |

| Nov.  |            | Further clarified the information in "Align Branch Targets in Program Hot Spots" on page 54.                                                                                                                                                       |  |  |  |

| 1999  |            | Further clarified the use of the REP instruction as filler in "Code Padding Using Neutral Code Fillers" on page 58.                                                                                                                                |  |  |  |

|       |            | Further clarified the information in "Use the PREFETCH 3DNow!™ Instruction" on page 79.                                                                                                                                                            |  |  |  |

|       |            | Modified examples 1 and 2 of "Unsigned Division by Multiplication of Constant" on page 116.                                                                                                                                                        |  |  |  |

|       |            | Added the optimization, "Efficient Implementation of Population Count Function" on page 136.                                                                                                                                                       |  |  |  |

|       |            | Further clarified the information in "Use FFREEP Macro to Pop One Register from the FPU Stack" on page 152.                                                                                                                                        |  |  |  |

|       |            | Further clarified the information in "Minimize Floating-Point-to-Integer Conversions" on page 154.                                                                                                                                                 |  |  |  |

xviii Revision History

| Date         | Rev     | Description                                                                                                                  |  |  |

|--------------|---------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| Nov.<br>1999 | E cont. | Added the optimization, "Check Argument Range of Trigonometric Instructions Efficiently" on page 157.                        |  |  |

|              |         | Added the optimization, "Take Advantage of the FSINCOS Instruction" on page 159.                                             |  |  |

|              |         | Further clarified the information in "Use 3DNow!™ Instructions for Fast Division" on page 162.                               |  |  |

|              |         | Further clarified the information in "Use FEMMS Instruction" on page 162.                                                    |  |  |

|              |         | Further clarified the information in "Use 3DNow!™ Instructions for Fast Square Root and Reciprocal Square Root" on page 165. |  |  |

|              |         | Clarified "3DNow!™ and MMX™ Intra-Operand Swapping" on page 169.                                                             |  |  |

|              |         | Corrected PCMPGT information in "Use MMX™ PCMP Instead of 3DNow!™ PFCMP" on page 173.                                        |  |  |

|              |         | Added the optimization, "Use MMX™ Instructions for Block Copies and Block Fills" on page 174.                                |  |  |

|              |         | Modified the rule for "Use MMX™ PXOR to Clear All Bits in an MMX Register" on page 185.                                      |  |  |

|              | D       | Modified the rule in "Use MMX™ PCMPEQD to Set All Bits in an MMX Register" on page 186.                                      |  |  |

|              |         | Added the optimization, "Optimized Matrix Multiplication" on page 187.                                                       |  |  |

| Oct.         |         | Added the optimization, "Efficient 3D-Clipping Code Computation Using 3DNow!™ Instructions" on page 190.                     |  |  |

| 1999         |         | Added the optimization, "Complex Number Arithmetic" on page 199.                                                             |  |  |

|              |         | Added Appendix E, "Programming the MTRR and PAT."                                                                            |  |  |

|              |         | Rearranged the appendixes.                                                                                                   |  |  |

|              |         | Added index.                                                                                                                 |  |  |

Revision History xix

22007K February 2002

xx Revision History

1

# Introduction

The AMD Athlon™ processor is the newest microprocessor in the AMD K86 family of microprocessors. The advances in the AMD Athlon processor take superscalar operation and out-of-order execution to a new level. The AMD Athlon processor has been designed to efficiently execute code written for previous-generation x86 processors. However, to enable the fastest code execution with the AMD Athlon processor, programmers should write software that includes specific code optimization techniques.

## **About This Document**

This document contains information to assist programmers in creating optimized code for the AMD Athlon processor. In addition to compiler and assembler designers, this document has been targeted to C and assembly-language programmers writing execution-sensitive code sequences.

This document assumes that the reader possesses in-depth knowledge of the x86 instruction set, the x86 architecture (registers and programming modes), and the IBM PC-AT platform.

This guide has been written specifically for the AMD Athlon processor, but it includes considerations for previous-

generation processors and describes how those optimizations are applicable to the AMD Athlon processor. This guide covers the following topics:

| Section   | Торіс                              | Description                                                                                                                                     |

|-----------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1 | Introduction                       | Outlines the material covered in this document. Summarizes the AMD Athlon™ microarchitecture.                                                   |

| Chapter 2 | Top Optimizations                  | Provides convenient descriptions of the most important optimizations a programmer should take into consideration.                               |

| Chapter 3 | C Source-Level Optimizations       | Describes optimizations that C/C++ programmers can implement.                                                                                   |

| Chapter 4 | Instruction Decoding Optimizations | Describes methods that will make<br>the most efficient use of the three<br>sophisticated instruction decod-<br>ers in the AMD Athlon processor. |

| Chapter 5 | Cache and Memory Optimizations     | Describes optimizations that make efficient use of the large L1 and L2 caches and high-bandwidth buses of the AMD Athlon processor.             |

| Chapter 6 | Branch Optimizations               | Describes optimizations that improve branch prediction and minimize branch penalties.                                                           |

| Chapter 7 | Scheduling Optimizations           | Describes optimizations that improve code scheduling for efficient execution resource utilization.                                              |

| Chapter 8 | Integer Optimizations              | Describes optimizations that improve integer arithmetic and make efficient use of the integer execution units in the AMD Athlon processor.      |

| Chapter 9 | Floating-Point Optimizations       | Describes optimizations that make maximum use of the superscalar and pipelined floatingpoint unit (FPU) of the AMD Athlon processor.            |

| Section    | Торіс                                               | Description                                                                                         |

|------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Chapter 10 | 3DNow!™ and MMX™ Optimizations                      | Describes code optimization guidelines for 3DNow!, MMX, and Enhanced 3DNow!/MMX.                    |

| Chapter 11 | General x86 Optimization Guidelines                 | Lists generic optimization techniques applicable to x86 processors.                                 |

| Appendix A | AMD Athlon™ Processor Microarchitecture             | Describes in detail the microar-<br>chitecture of the AMD Athlon<br>processor.                      |

| Appendix B | Pipeline and Execution Unit<br>Resources Overview   | Describes in detail the execution unit and its relation to the instruction pipeline.                |

| Appendix C | Implementation of Write Combining                   | Describes the algorithm used by the AMD Athlon processor to write-combine.                          |

| Appendix D | Performance-Monitoring Counters                     | Describes the usage of the performance counters available in the AMD Athlon processor.              |

| Appendix E | Programming the MTRR and PAT                        | Describes the steps needed to program the Memory Type Range Registers and the Page Attribute Table. |

| Appendix F | Instruction Dispatch and Execution Resources/Timing | Lists the instruction execution resource usage and its latency.                                     |

## **AMD Athlon™ Processor Family**

The AMD Athlon processor family uses state-of-the-art decoupled decode/execution design techniques to deliver next-generation performance with x86 binary software compatibility. This next-generation processor family advances x86 code execution by using flexible instruction predecoding, wide and balanced decoders, aggressive out-of-order execution, parallel integer execution pipelines, parallel floating-point execution pipelines, deep pipelined execution for higher delivered operating frequency, dedicated cache memory, and a new high-performance double-rate 64-bit local bus.

As an x86 binary-compatible processor, the AMD Athlon processor implements the industry-standard x86 instruction set

by decoding and executing the x86 instructions using a proprietary microarchitecture. This microarchitecture allows the delivery of maximum performance when running x86-based PC software.

# AMD Athlon™ Processor Microarchitecture Summary

The AMD Athlon processor brings superscalar performance and high operating frequencies to computer systems running industry-standard x86 software. A brief summary of the next-generation design features implemented in the AMD Athlon processor is as follows:

- High-speed double-rate local-bus interface

- Large, split 128-Kbyte level-one (L1) cache

- External level-two (L2) cache on Models 1 and 2

- On-die L2 cache on Models 3, 4, and 6

- Dedicated level-two (L2) cache

- Instruction predecode and branch detection during cacheline fills

- Decoupled decode/execution core

- Three-way x86 instruction decoding

- Dynamic scheduling and speculative execution

- Three-way integer execution

- Three-way address generation

- Three-way floating-point execution

- 3DNow!<sup>TM</sup> technology and MMX<sup>TM</sup> single-instruction multiple-data (SIMD) instruction extensions

- Super data forwarding

- Deep out-of-order integer and floating-point execution

- Register renaming

- Dynamic branch prediction

The AMD Athlon processor communicates through a next-generation high-speed local bus that is beyond the current Socket 7 or Super7<sup>TM</sup> bus standard. The local bus can transfer data at twice the rate of the bus operating frequency by using both the rising and falling edges of the clock (see

"AMD Athlon<sup>TM</sup> System Bus" on page 214 for more information).

To reduce on-chip cache-miss penalties and to avoid subsequent data-load or instruction-fetch stalls, the AMD Athlon processor has a dedicated high-speed L2 cache. The large 128-Kbyte L1 on-chip cache and the L2 cache allow the AMD Athlon execution core to achieve and sustain maximum performance.

As a decoupled decode/execution processor, the AMD Athlon processor makes use of a proprietary microarchitecture, which defines the heart of the AMD Athlon processor. With the inclusion of all these features, the AMD Athlon processor is capable of decoding, issuing, executing, and retiring multiple x86 instructions per cycle, resulting in superior scalable performance.

The AMD Athlon processor includes both the industry-standard MMX SIMD integer instructions and the 3DNow! SIMD floating-point instructions that were first introduced in the AMD-K6®-2 processor. The design of 3DNow! technology is based on suggestions from leading graphics vendors and independent software vendors (ISVs). Using SIMD format, the AMD Athlon processor can generate up to four 32-bit, single-precision floating-point results per clock cycle.

The 3DNow! execution units allow for high-performance floating-point vector operations, which can replace x87 instructions and enhance the performance of 3D graphics and other floating-point-intensive applications. Because the 3DNow! architecture uses the same registers as the MMX instructions, switching between MMX and 3DNow! has no penalty.

The AMD Athlon processor designers took another innovative step by carefully integrating the traditional x87 floating-point, MMX, and 3DNow! execution units into one operational engine. With the introduction of the AMD Athlon processor, the switching overhead between x87, MMX, and 3DNow! technology is virtually eliminated. The AMD Athlon processor combined with 3DNow! technology brings a better multimedia experience to mainstream PC users while maintaining backward compatibility with all existing x86 software.

Although the AMD Athlon processor can extract code parallelism on-the-fly from off-the-shelf, commercially available x86 software, specific code optimization for the AMD Athlon processor can result in even higher delivered performance. This document describes the proprietary microarchitecture in the AMD Athlon processor and makes recommendations for optimizing execution of x86 software on the processor.

The coding techniques for achieving peak performance on the AMD Athlon processor include, but are not limited to, those for the AMD-K6®, AMD-K6-2, Pentium®, Pentium Pro, and Pentium II processors. However, many of these optimizations are not necessary for the AMD Athlon processor to achieve maximum performance. Due to the more flexible pipeline control and aggressive out-of-order execution, the AMD Athlon processor is not as sensitive to instruction selection and code scheduling. This flexibility is one of the distinct advantages of the AMD Athlon processor.

The AMD Athlon processor uses the latest in processor microarchitecture design techniques to provide the highest x86 performance for today's computer. In short, the AMD Athlon processor offers true next-generation performance with x86 binary software compatibility.

2

# **Top Optimizations**

This chapter contains descriptions of the best optimizations for improving the performance of the AMD Athlon<sup>TM</sup> processor. Subsequent chapters contain more detailed descriptions of these and other optimizations. The optimizations in this chapter are divided into two groups and listed in order of importance.

# Group I—Essential Optimizations

Group I contains essential optimizations. Users should follow these critical guidelines closely. The optimizations in Group I are as follows:

- Memory Size and Alignment Issues—Avoid memory size mismatches—Align data where possible

- Use the PREFETCH 3DNow!<sup>TM</sup> Instruction

- Select DirectPath Over VectorPath Instructions

# Group II—Secondary Optimizations

Group II contains secondary optimizations that can significantly improve the performance of the AMD Athlon processor. The optimizations in Group II are as follows:

- Load-Execute Instruction Usage—Use Load-Execute instructions—Avoid load-execute floating-point instructions with integer operands

- Take Advantage of Write Combining

- Optimization of Array Operations With Block Prefetching

- Use 3DNow! Instructions

- Recognize 3DNow! Professional Instructions

- Avoid Branches Dependent on Random Data

- Avoid Placing Code and Data in the Same 64-Byte Cache Line

# **Optimization Star**

The top optimizations described in this chapter are flagged with a star. In addition, the star appears beside the more detailed descriptions found in subsequent chapters.

# **Group I Optimizations—Essential Optimizations**

## **Memory-Size and Alignment Issues**

#### **Avoid Memory-Size Mismatches**

Avoid memory-size mismatches when different instructions operate on the same data. When an instruction stores and another instruction reloads the same data, keep their operands aligned and keep the loads/stores of each operand the same size. The following code examples result in a store-to-load-forwarding (STLF) stall:

#### **Example 1 (Avoid):**

```

MOV DWORD PTR [F00], EAX

MOV DWORD PTR [F00+4], EDX

FLD QWORD PTR [F00]

```

Avoid large-to-small mismatches, as shown in the following code:

#### **Example 2 (Avoid):**

```

FST QWORD PTR [F00]

MOV EAX, DWORD PTR [F00]

MOV EDX, DWORD PTR [F00+4]

```

#### **Align Data Where Possible**

Avoid misaligned data references. All data whose size is a power of two is considered aligned if it is *naturally* aligned. For example:

- Word accesses are aligned if they access an address divisible by two.

- Doubleword accesses are aligned if they access an address divisible by four.

- Quadword accesses are aligned if they access an address divisible by eight.

- TBYTE accesses are aligned if they access an address divisible by eight.

A misaligned store or load operation suffers a minimum onecycle penalty in the AMD Athlon processor load/store pipeline. In addition, using misaligned loads and stores increases the likelihood of encountering a store-to-load forwarding pitfall. For a more detailed discussion of store-to-load forwarding issues, see "Store-to-Load Forwarding Restrictions" on page 86.

## Use the 3DNow!™ Prefetching Instructions

For code that can take advantage of prefetching, use the 3DNow! PREFETCH and PREFETCHW instructions to increase the effective bandwidth of the AMD Athlon processor, thereby significantly improving performance. All the prefetch instructions are essentially integer instructions and can be used anywhere, in any type of code (for example, integer, x87, 3DNow!, MMX). Use the following formula to determine prefetch distance:

## Prefetch Distance = $200 \times (^{DS}/_{C})$

- Round up to the nearest cache line.

- DS is the data stride per loop iteration.

- C is the number of cycles per loop iteration when hitting in the L1 cache.

See "Use the PREFETCH 3DNow!<sup>TM</sup> Instruction" on page 79 for more details.

#### **Select DirectPath Over VectorPath Instructions**

Use DirectPath instructions rather than VectorPath instructions. DirectPath instructions are optimized for decode and execute efficiently by minimizing the number of operations per x86 instruction, which includes 'register ← register op memory' as well as 'register ← register op register' forms of instructions. Up to three DirectPath instructions can be decoded per cycle. VectorPath instructions block the decoding of DirectPath instructions.

The AMD Athlon processor implements the majority of instructions used by a compiler as DirectPath instructions. Nevertheless, assembly writers must still take into consideration the usage of DirectPath versus VectorPath instructions.

See Appendix F, "Instruction Dispatch and Execution Resources/Timing," for tables of DirectPath and VectorPath instructions.

# **Group II Optimizations—Secondary Optimizations**

## **Load-Execute Instruction Usage**

#### **Use Load-Execute Instructions**

Most load-execute integer instructions are DirectPath decodable and can be decoded at the rate of three per cycle. Splitting a load-execute integer instruction into two separate instructions—a load instruction and a "reg, reg" instruction—reduces decoding bandwidth and increases register pressure, which results in lower performance. Use the split-instruction form to avoid scheduler stalls for longer executing instructions and to explicitly schedule the load and execute operations.

#### **Use Load-Execute Floating-Point Instructions with Floating-Point Operands**

When operating on single-precision or double-precision floating-point data, wherever possible use floating-point loadexecute instructions to increase code density.

**Note:** This optimization applies only to floating-point instructions with floating-point operands and not to integer operands, as described in the next section.

This coding style helps in two ways. First, denser code allows more work to be held in the instruction cache. Second, the denser code generates fewer internal MacroOPs, allowing the FPU scheduler to hold more work, which increases the chances of extracting parallelism from the code.

#### **Example 1 (Avoid):**

| FLD   | QWORD | PTR  | [TEST1] |

|-------|-------|------|---------|

| FLD   | QWORD | PTR  | [TEST2] |

| FMIII | TZ TZ | r(1) |         |

#### **Example 1 (Preferred):**

| FLD  | QWORD | PTR | [TEST1] |

|------|-------|-----|---------|

| FMUL | QWORD | PTR | [TEST2] |

#### **Avoid Load-Execute Floating-Point Instructions with Integer Operands**

Do not use load-execute floating-point instructions with *integer* operands: FIADD, FISUB, FISUBR, FIMUL, FIDIV, FIDIVR, FICOM, and FICOMP. Remember that floating-point instructions can have integer operands, while integer instructions cannot have floating-point operands.

Use separate FILD and arithmetic instructions for floating-point computations involving integer-memory operands. This optimization has the potential to increase decode bandwidth and OP density in the FPU scheduler. The floating-point load-execute instructions with integer operands are VectorPath and generate two OPs in a cycle, while the discrete equivalent enables a third DirectPath instruction to be decoded in the same cycle. In some situations, this optimization can also reduce execution time if the FILD can be scheduled several instructions ahead of the arithmetic instruction in order to cover the FILD latency.

#### **Example 2 (Avoid):**

FLD QWORD PTR [foo] FIMUL DWORD PTR [bar] FIADD DWORD PTR [baz]

#### **Example 2 (Preferred):**

FILD DWORD PTR [bar]

FILD DWORD PTR [baz]

FLD QWORD PTR [foo]

FMULP ST(2), ST

FADDP ST(1),ST

## **Take Advantage of Write Combining**

This guideline applies only to operating-system, device-driver, and BIOS programmers. In order to improve system performance, the AMD Athlon processor aggressively combines multiple memory-write cycles of any data size that address locations within a 64-byte cache line aligned write buffer.

See Appendix C, "Implementation of Write Combining," for more details.

## **Optimizing Main Memory Performance for Large Arrays**

# Reading Large Arrays and Streams

To process a large array (200 Kbytes or more), or other large sequential data sets that are not already in cache, use block prefetch to achieve maximum performance. The block prefetch technique involves processing the data in blocks. The data for each block is preloaded into the cache by reading just one address per cache line, causing each cache line to be filled with the data from main memory.

Filling the cache lines in this manner, with a single read operation per line, allows the memory system to burst the data at the highest achievable read bandwidth.

Once the input data is in cache, the processing can then proceed at the maximum instruction execution rate, because no memory read accesses will slow down the processor.

# Writing Large Arrays to Memory

If data needs to be written back to memory during processing, a similar technique can be used to accelerate the write phase. The processing loop writes data to a temporary in-cache buffer, to avoid memory-access cycles and to allow the processor to execute at the maximum instruction rate. Once a complete data block has been processed, the results are copied from the incache buffer to main memory, using a loop that employs the very fast streaming store instruction, MOVNTQ.

See "Optimizing Main Memory Performance for Large Arrays" on page 66 for detailed optimization examples, where the block-prefetch method is used for simply copying memory, and also for adding two floating-point arrays through the use of the x87 floating-point unit.

Also see the complete optimized memcpy routine in "Use MMX<sup>TM</sup> Instructions for Block Copies and Block Fills" on page 174. This example employs Block Prefetch for large size memory blocks.

#### Use 3DNow!™ Instructions

When single precision is required, perform floating-point computations using the 3DNow! instructions instead of x87 instructions. The SIMD nature of 3DNow! instructions achieves twice the number of FLOPs that are achieved through x87 instructions. 3DNow! instructions also provide for a flat register file instead of the stack-based approach of x87 instructions.

See Table 23 on page 298 for a list of 3DNow! instructions. For information about instruction usage, see the  $3DNow!^{TM}$  Technology Manual, order no. 21928.

### **Recognize 3DNow! Professional Instructions**